Принята вторая версия стандарта Hybrid Memory Cube

Так исторически сложилось, что процессоры развивались быстрее, чем совершенствовался интерфейс памяти. В итоге отрасль упёрлась в так называемую «стену памяти» (memory wall), когда пропускная способность при работе с подсистемой памяти стала отставать от скорости запроса процессора к данным в ОЗУ. В феврале 2011 года компания Micron предложила «пробить стену памяти» с помощью переноса контроллера памяти в микросхему памяти. При этом саму память также следовало видоизменить, значительно расширив ширину шины данных. Значительно! Комитет JEDEC назвал такую память High Bandwidth Memory (HBM), а компания Micron — Hybrid Memory Cube (HMC), хотя обе версии — это фактически одно и то же.

По понятным причинам память HMC (HBM) с шиной данных шириной от 1024 бит и выше так просто к процессору не подключить. Поэтому межчиповый интерфейс предложен в виде последовательной шины. Именно этим занят перенесённый в состав микросхемы памяти контроллер памяти. Он преобразует широкополосный доступ к кристаллам памяти в последовательный высокоскоростной канал передачи к процессору (что не исключает необходимость в собственном контроллере памяти в составе процессора). Зато даже в первом поколении микросхем Micron HMC каждая микросхема может передавать в процессор данные со скоростью до 160 Гбайт/с.

Память Microm HMC пропишется в составе ускорителей Intel Xeon Phi образца 2015 года

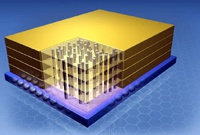

Вторая версия стандарта Hybrid Memory Cube, чистовые спецификации которой были на днях опубликованы на сайте консорциума Hybrid Memory Cube Consortium (HMCC), обещает появление микросхем HMC с максимальной пропускной способностью до 480 Гбайт/с (в зависимости от организации интерфейса). Для этого скорость по одной линии интерфейса HMC увеличена с максимального значения 15 Гбит/с до 30 Гбит/с. В общем случае микросхемы HMC представляют собой четыре вертикально уложенные друг на друга кристалла памяти, соединённые с нижним пятым слоем — контроллером — с помощью сквозных вертикальных соединений TSVs. В настоящий момент память HMC поддерживают однокристальные сборки и FPGA-матрицы компании Altera, чипсеты для серверных платформ Fujitsu, а также процессоры Intel Xeon Phi в поколении Knights Landing. В разновидности памяти HBM технология доступа к широкополосной памяти будет поддержана компаниями AMD и NVIDIA. Но это уже другая история.